# **V93XX Datasheet**

Specifications are subject to change without notice.

© 2021 HangzhouVango Technologies, Inc.

This document contains information that is proprietary to Vango Technologies, Inc. Unauthorized reproduction of this information in whole or in part is strictly prohibited.

### **Revision History**

| Date       | Version | Description                                                                                                              |  |

|------------|---------|--------------------------------------------------------------------------------------------------------------------------|--|

| 2019.07.19 | 2.0     | Initial release                                                                                                          |  |

| 2020.11.25 | 2.1     | Modify the description of SYS_STS register.                                                                              |  |

|            | 3.1     | Modify ANA_CTRL0 BIT13 and BIT14 function                                                                                |  |

|            |         | Modify ANA_CTRL1 BIT7 and BIT23 function                                                                                 |  |

|            |         | Add pull-up resistance to TX, RX and RSTN pin                                                                            |  |

| 2020.02.18 |         | When the RSTN pin remains low for a certain period of time, the chip will be reset. The time was changed from 1ms to 2ms |  |

|            |         | Open the input short circuit function of voltage channel and current channel                                             |  |

|            |         | On-chip reference voltage changed to 1.21v                                                                               |  |

|            |         | The power supply voltage range is changed to 2.6 $\sim$ 3.6V                                                             |  |

|            |         | The power down threshold voltage is changed to 2.6 $\sim$ 3.1V                                                           |  |

### Content

| Rev | vision  | Histo  | ry                                 | 1  |

|-----|---------|--------|------------------------------------|----|

| Fig | ure Li  | st     |                                    | 5  |

| Tał | ole Lis | st     |                                    | 7  |

| 1.  | G       | eneral | Description1                       | 0  |

|     | 1.1.    | Functi | ional Block Diagram 1              | .1 |

|     | 1.2.    |        | escription 1                       |    |

|     | 1       |        | V9381 Pin Description 1            |    |

|     | 1       | .2.2.  | V9360 Pin Description 1            | .3 |

|     | 1       | .2.3.  | Pin Description 1                  | .3 |

|     | 1.3.    | Param  | neters                             | .5 |

|     | 1.4.    | Absolu | ute Maximum Ratings                | .6 |

| 2.  | R       | egiste | rs1                                | 7  |

|     | 2.1.    | Regist | ters List                          | .7 |

|     | 2.2.    |        | g Control Registers 2              |    |

|     | 2       |        | ANA_CTRL0 Register 2               |    |

|     | _       |        | ANA_CTRL1 Register                 |    |

|     | 2.3.    | Syste  | m Control & Status Register 2      |    |

|     | 2       | .3.1.  | SYS_BAUDCNT1 Register              | 25 |

|     |         | .3.2.  | SYS_BAUDCNT8 Register              |    |

|     |         |        | SYS_ INTSTS Register               |    |

|     | 2       | .3.4.  | SYS_INTEN Register                 | 29 |

|     | 2       | .3.5.  | SYS_STS Register                   | 32 |

|     | 2       | .3.6.  | SYS_MISC Register                  |    |

|     | 2       | .3.7.  | SYS_BLKX Register                  |    |

|     |         | .3.8.  | SYS_IOCFGXX Register               |    |

|     | 2       | .3.9.  | SYS_VERSION Register               | 1  |

|     |         |        | ing Control Registers 4            | 1  |

|     | 2       | .4.1.  | DSP_CTRL0 Register                 | 1  |

|     | 2       | .4.2.  | DSP_CTRL1 Register                 | -5 |

|     | 2       | .4.3.  | DSP_CTRL2 Register                 | 8  |

|     | 2       | .4.4.  | DSP_CTRL3 Register                 | 52 |

|     | 2       | .4.5.  | DSP_CTRL4 Register                 |    |

|     | 2       | .4.6.  | DSP_CTRL5 Register                 | 57 |

|     | 2.5.    | Meter  | ing Data Register5                 | ;9 |

|     | 2       | .5.1.  | DC Component Register              |    |

|     | 2       | .5.2.  | RMS Register                       | 50 |

|     | 2       |        | Active/ Reactive Power Register    |    |

|     | 2       | .5.4.  | Fundamental Wave Channel Register6 | 52 |

|     | 2       | .5.5.  | Line Frequency Register            | 52 |

|     | 2.6.    | -      | y Accumulator Register6            |    |

|     | 2.7.    | Phase  | Measurement Register               | 53 |

|     | 2.8.    | Power  | -creep Threshold Register6         | 54 |

|    | 2.9.         | Voltage Swell or Dip Threshold Register |      |

|----|--------------|-----------------------------------------|------|

|    | 2.10.        | Fast Detection Threshold Register       |      |

|    | 2.11.        | 5                                       |      |

|    | 2.12.        |                                         |      |

|    |              | .12.1. DC Bias Setting Register         |      |

|    |              | .12.2. RMS Calibration Register         |      |

|    |              | .12.3. Power Calibration Register       |      |

|    |              | .12.4. Threshold Register               |      |

|    | 2.           | .12.5. Phase Calibration Register       | . 69 |

|    | 2.           | .12.6. Bandpass Filter Register         | . 69 |

|    | 2.13.        | Checksum Register                       | . 70 |

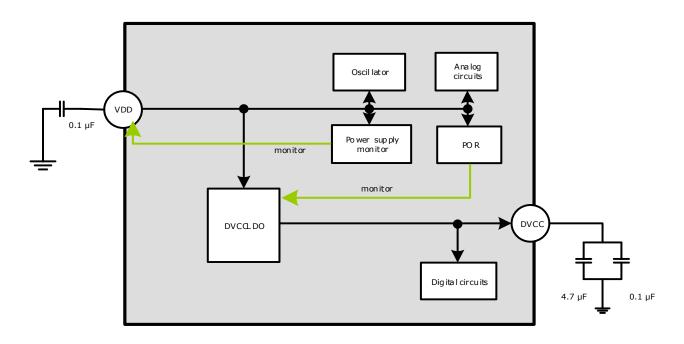

| 3. | Μ            | lain Power Supply                       | .73  |

|    | 3.1.         | Power Supply Monitoring Circuit         | . 73 |

|    | 3.2.         | Digital Power Supply                    | . 74 |

|    | 3.3.         | Power on Reset Circuit                  | . 74 |

| 4. | В            | andgap circuit                          | .75  |

| _  |              |                                         |      |

| 5. |              |                                         |      |

|    | 5.1.         | External input high-frequency clock     |      |

|    | 5.2.         | High-Frequency RC Oscillator            |      |

|    | 5.3.         | Low-Frequency RC Oscillator             |      |

|    | 5.4.         | External Input Clock                    | . 79 |

| 6. | R            | ESET                                    | .80  |

|    | 6.1.         | Reset Related Registers                 | . 80 |

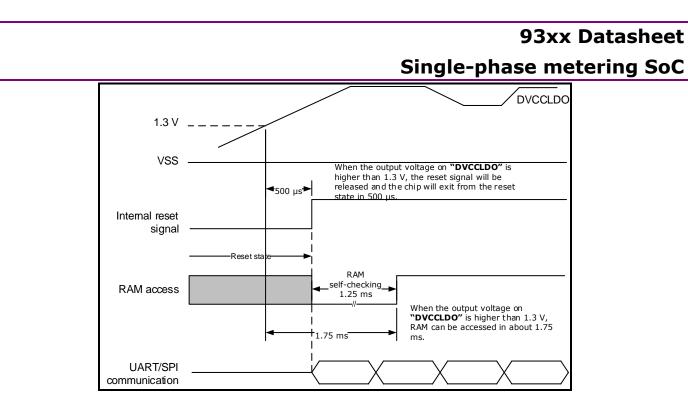

|    | 6.2.         | Power-On Reset (POR)                    | . 80 |

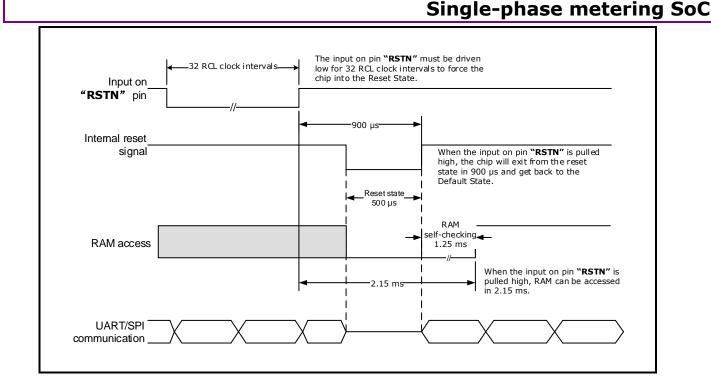

|    | 6.3.         | External Reset                          | . 81 |

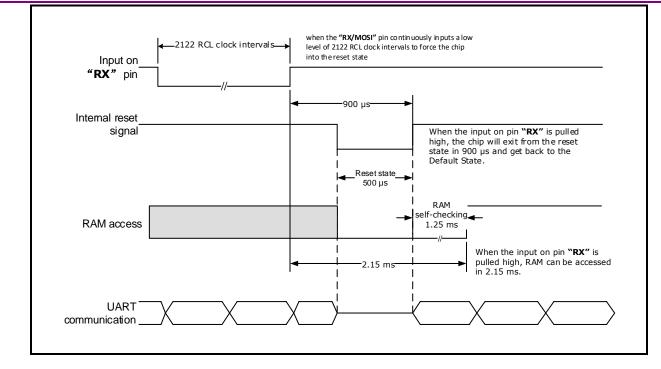

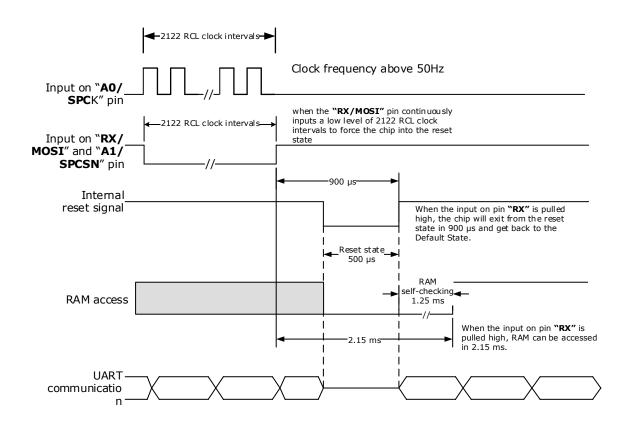

|    | 6.4.         | RX Reset                                | . 82 |

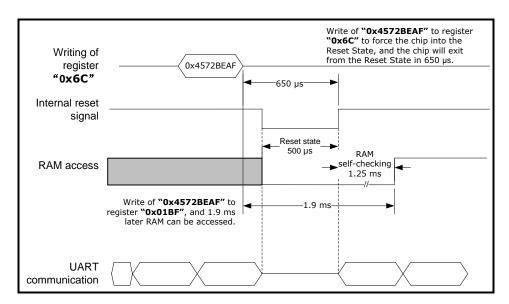

|    | 6.5.         | Global Software Reset                   | . 84 |

| 7. | U            | ART                                     | .85  |

|    | 7.1.         | Overview                                | . 85 |

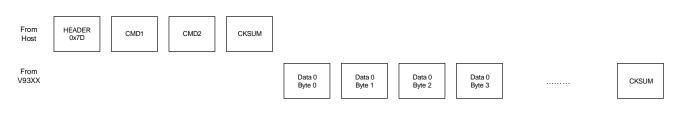

|    | 7.2.         | Broadcast Communication                 | . 85 |

|    | 7.3.         | Read Operation                          | . 87 |

|    | 7.4.         | Write Operation                         | . 89 |

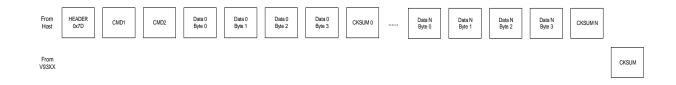

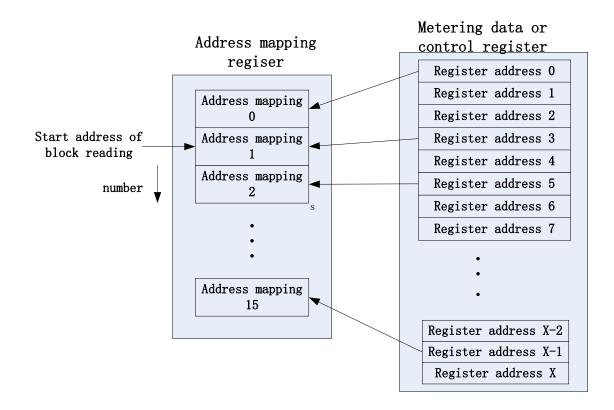

|    | 7.5.         | Block Reading Operation                 | . 91 |

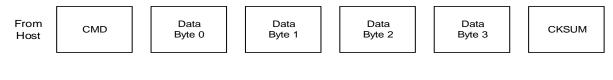

| 8. | S            | PI                                      | .94  |

|    | 8.1.         | Overview                                | . 94 |

|    | 8.2.         | Write Operation                         |      |

|    | 8.3.         | Read Operation                          |      |

|    | 8.4.         | Initialize interface                    |      |

|    | 8.5.         | 4-wire SPI Mode                         |      |

|    | 8.6.         | 3-wire SPI Mode                         |      |

| ~  |              |                                         |      |

| 9. | D            | SP                                      |      |

|    | 0 1          | Oversiew                                | ~~   |

|    | 9.1.<br>9.2. | Overview<br>Features                    |      |

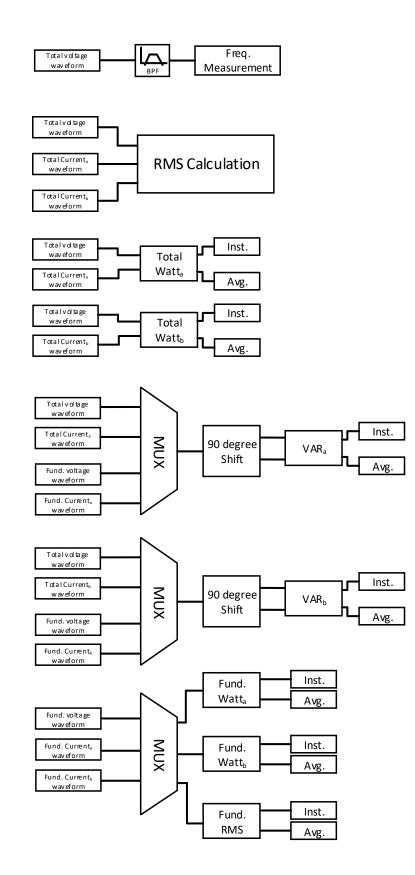

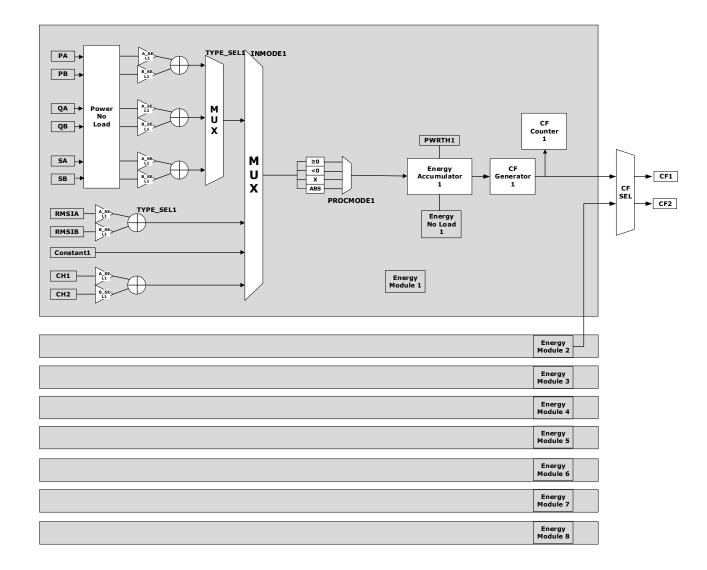

|     | 9.3.  | Funct   | ional Diagram                                               | 100 |

|-----|-------|---------|-------------------------------------------------------------|-----|

|     | 9.4.  | Applic  | cation Description                                          | 102 |

|     | 9.    | 4.1.    | Phase Calibration                                           | 102 |

|     | 9.    | 4.2.    | Frequency Calculation                                       | 102 |

|     | 9.    | 4.3.    | Phase Test                                                  | 103 |

|     | 9.    | 4.4.    | Power-creep Detection                                       | 103 |

| 10  | Δ     | ctive \ | Waveform upload and buffer                                  | 104 |

|     | 10.1. |         | ive Waveform upload                                         |     |

|     |       | 0.1.1.  | Overview                                                    |     |

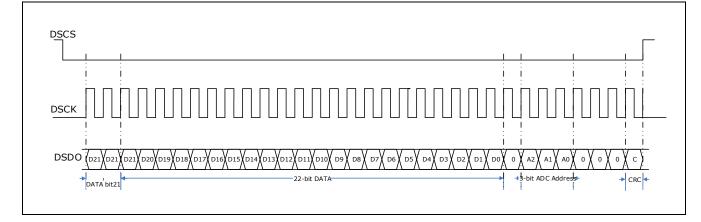

|     |       | 0.1.2.  | Timing and Format                                           |     |

|     | 10.2. |         | veform Buffer                                               |     |

|     |       |         |                                                             |     |

| 11. |       |         | al Signal monitoring                                        |     |

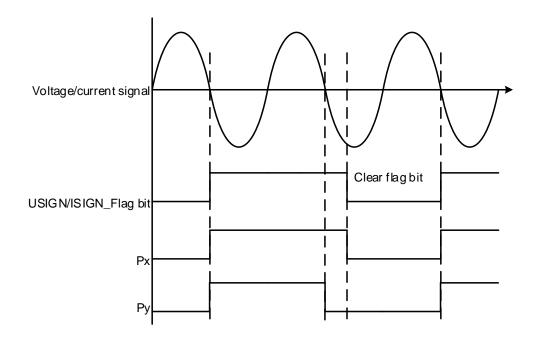

|     | 11.1. |         | o-crossing Detection                                        |     |

|     | 11.2. | Volt    | tage Swell/Dip                                              | 108 |

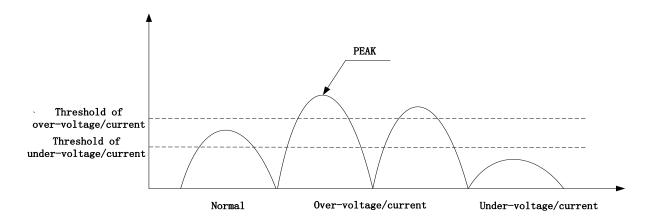

|     | 11.3. | Ove     | er-voltage and under-voltage/Over-current and under-current | 108 |

| 12  | . Ei  | nergy   | Accumulator                                                 | 110 |

|     | 12.1. | Higl    | h-speed Energy Accumulator                                  | 111 |

|     | 12.2. | Low     | y-speed Energy Accumulator                                  | 111 |

|     | 12.3. | CF      | Output                                                      | 112 |

|     | 12.4. | Ene     | ergy Accumulator Power-creep Detection                      | 112 |

|     | 12.5. | Acti    | ive Accumulation uploading Interface                        | 113 |

| 13  | S     | ignal ] | IO Ports                                                    | 114 |

|     | 13.1. | -       | erview                                                      |     |

|     | 13.2. |         | ictional Description                                        |     |

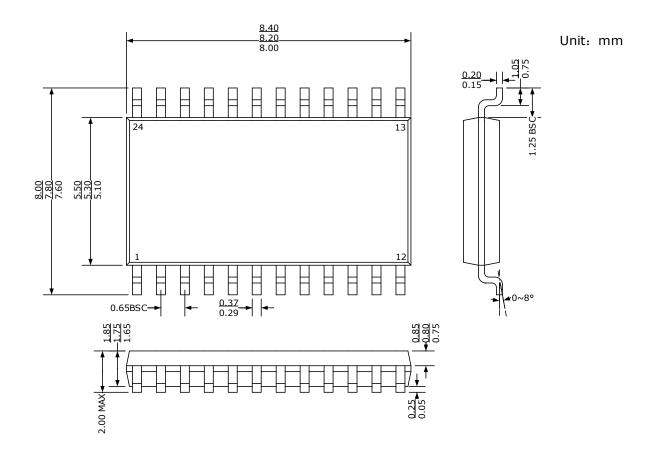

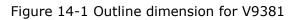

| 14  | •     | utlina  | Dimensions                                                  | 116 |

| T.4 |       | utime   |                                                             | TTO |

### **Figure List**

| Figure 1-1 Functional block diagram11                                                |

|--------------------------------------------------------------------------------------|

| Figure 1-2 V9381 Pin Description12                                                   |

| Figure 1-3 V9360 Pin Description13                                                   |

| Figure 3-1 Main Power System73                                                       |

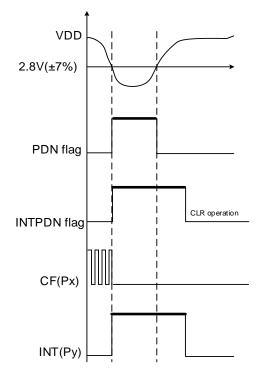

| Figure 3-2 Power-down monitoring74                                                   |

| Figure 4-1 Register for Bandgap Circuit75                                            |

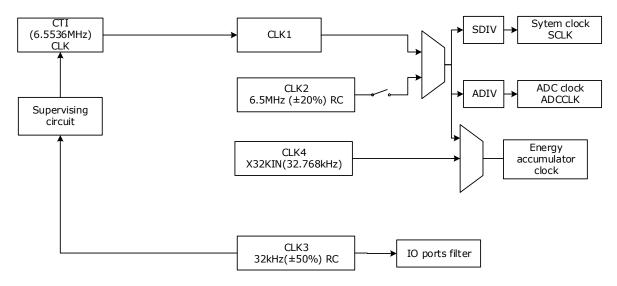

| Figure 5-1 Clock generation77                                                        |

| Figure 6-1 Timing for POR81                                                          |

| Figure 6-2 Timing for RSTN82                                                         |

| Figure 6-3 Timing for RX Reset of UART83                                             |

| Figure 6-4 Timing for RX Reset of SPI83                                              |

| Figure 6-5 Timing of Global Software Reset84                                         |

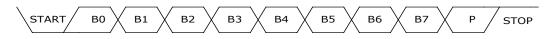

| Figure 7-1 Structure of an 11-Bit data byte (from LSB to MSB)85                      |

| Figure 7-2 command frame for broadcast writing operation                             |

| Figure 7-3 Communication protocol for read operation87                               |

| Figure 7-4 Communication protocol for write operation                                |

| Figure 7-5 address mapping for block reading91                                       |

| Figure 7-6 Communication protocol for block reading operation92                      |

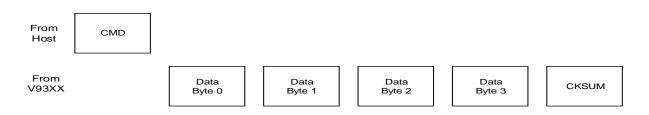

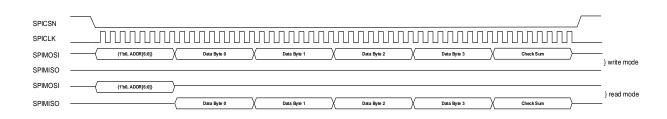

| Figure 8-1 Communication protocol for SPI write operation95                          |

| Figure 8-2 Communication protocol for SPI read operation95                           |

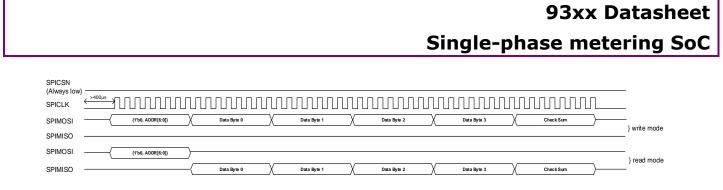

| Figure 8-3 Communication protocol for 4 wire SPI mode97                              |

| Figure 8-4 Communication protocol for 3 wire SPI mode98                              |

| Figure 9-1 Functional Diagram1 of Metering DSP100                                    |

| Figure 9-2 Functional Diagram2 of Metering DSP101                                    |

| Figure 10-1 Communication timing of DMA SPI105                                       |

| Figure 11-1 output waveform for voltage/current zero-crossing                        |

| Figure 11-2 Over-voltage and under-voltage/Over-current and under-current detect 108 |

| Figure 12-1 Functional block diagram of energy bucket110                             |

| Figure 13-1 Functional Block Diagram of signal IO ports115                           |

####

### **Table List**

| Table 1-1 Pin description                                                         |

|-----------------------------------------------------------------------------------|

| Table 1-2 Parameters   15                                                         |

| Table 1-3 Absolute maximum ratings       16                                       |

| Table 2-1 Register list    17                                                     |

| Table 2-2 Analog Control Register 0 (0x00, ANA_CTRL0)22                           |

| Table 2-3 Analog Control Register 1 (0x01, ANA_CTRL1)22                           |

| Table 2-4 UART transmitting data 1bit count value (0x70, SYS_BAUDCNT1)         25 |

| Table 2-5 UART receiving data 8bit count value (0x71, SYS_BAUDCNT8)         25    |

| Table 2-6 System Interrupt Register (0x72, SYS_INTSTS)25                          |

| Table 2-7 System Interrupt Enable Register (0x73, SYS_INTEN)       29             |

| Table 2-8 System Status Register (0x74, SYS_STS)       32                         |

| Table 2-9 System Control Register (0x75, SYS_MISC)       36                       |

| Table 2-10 Block-reading Address Register 0 (0x79, SYS_BLK0_ADDR)         37      |

| Table 2-11 Block-reading Address Register 1 (0x7A, SYS_BLK1_ADDR)         37      |

| Table 2-12 Block-reading Address Register 2 (0x7B, SYS_BLK2_ADDR)         37      |

| Table 2-13 Block-reading Address Register 3 (0x7C, SYS_BLK3_ADDR)         37      |

| Table 2-14 IO Configuration Register 0 (0x7D, SYS_IOCFGX0)       38               |

| Table 2-15 P0CFG Bit[5:0] Description38                                           |

| Table 2-16 IO Configuration Register 1 (0x7E, SYS_IOCFGX1)       40               |

| Table 2-17 Version Information Register (0x7F, SYS_VERSION)         41            |

| Table 2-18 Metering Control Register 0 (0x02, DSP_CTRL0)       41                 |

| Table 2-19 Metering Control Register 2 (0x03, DSP_CTRL1)       45                 |

| Table 2-20 Metering Control Register 2 (0x04, DSP_CTRL2)       48                 |

| Table 2-21 Metering Control Register 3 (0x05, DSP_CTRL3)       52                 |

| Table 2-22 Metering Control Register 4 (0x06, DSP_CTRL4)       55                 |

| Table 2-23 Metering Control Register 5 (0x07, DSP_CTRL5)                          |

| Table 2-24 DC Component Register       60                                         |

| Table 2-25 Voltage/ Current/ Measurement Signal (M) RMS Register60                |

| Table 2-26 Active/ Reactive Power Register61                                      |

| Single-phase | metering | SoC |

|--------------|----------|-----|

|--------------|----------|-----|

| Table 2-27 Fundamental Wave Channel Instantaneous Register         62                                           |

|-----------------------------------------------------------------------------------------------------------------|

| Table 2-28 Fundamental Wave Channel Average Register                                                            |

| Table 2-29 Line Frequency Register (0x21, DSP_DAT_FRQ)       62                                                 |

| Table 2-30 Energy Accumulator Register62                                                                        |

| Table 2-31 Phase Measurement Register63                                                                         |

| Table 2-32 Power-creep Threshold Register64                                                                     |

| Table 2-33 Voltage Swell or Dip Threshold Register       64                                                     |

| Table 2-34 Fast detection Threshold Register         65                                                         |

| Table 2-35 Waveform Data Register65                                                                             |

| Table 2-36 DC Bias Setting Register       66                                                                    |

| Table 2-37 Voltage/ Current/ Measurement RMS Calibration Register                                               |

| Table 2-38 Total-wave Active/ Reactive Power Calibration Register         67                                    |

| Table 2-39 Threshold Register                                                                                   |

| Table 2-40 Phase Calibration Register (0x33, DSP_CFG_PHC)                                                       |

| Table 2-41 Bandpass Filter Register (0x37, DSP_CFG_BPF)69                                                       |

| Table 2-42 Checksum Register (0x38, DSP_CFG_CKSUM)       70                                                     |

| Table 2-43 Self-checking Register       70                                                                      |

| Table 5-1 Clock Generation Related Registers         77                                                         |

| Table 6-1 Reset Related Registers80                                                                             |

| Table 7-1 UART communication errors    85                                                                       |

| Table 7-2 Structure of Data Byte (B7:B0) From Master MCU to V93XX on Broadcast         Operation       86       |

| Table 7-3 Structure of Data Byte (B7:B0) From Master MCU to V93XX on Read Operation87                           |

| Table 7-4 Structure of Data Byte (B7:B0) From V93XX to Master MCU on read Operation88                           |

| Table 7-5 Structure of Data Byte (B7:B0) From Master MCU to V93XX on Write Operation 89                         |

| Table 7-6 Structure of Data Byte (B7:B0) From V93XX to Master MCU on Write Operation 90                         |

| Table 7-7 Structure of Data Byte (B7:B0) From Master MCU to V93XX on block reading         Operation         92 |

| Table 7-8 Structure of Data Byte (B7:B0) From V93XX to Master MCU on block reading         Operation         93 |

| Table 8-1 SPI communication errors       94                                                                     |

| Table 8-2 Structure of Data Byte (B7:B0) From Master MCU to V93XX on write Operation95                          |

| Table 8-3 Structure of Data Byte (B7:B0) From Master MCU to V93XX on read Operation95 |

|---------------------------------------------------------------------------------------|

| Table 8-4 Structure of Data Byte (B7:B0) From V93XX to Master MCU on read Operation96 |

| Table 9-1 Phase Calibration Description         102                                   |

| Table 9-2 Frequency register source FRQ_SEL description         102                   |

| Table 9-3 Frequency Constant Description         103                                  |

| Table 10-1 Active waveform data upload configuration104                               |

| Table 10-2 Active waveform data upload format         105                             |

| Table 10-3 waveform buffer data format106                                             |

### **1.General Description**

The V93XX is a single-phase metering chip which supports the total-wave and fundamental-wave of various modes and supports various power grids to monitor events. Furthermore, the waveform data can be transmitted via DMA by SPI protocol, or storage locally through the waveform buffer.

- Main Power: 3.3V power supply, voltage input range 2.6v to 3.6V.

- Reference voltage: 1.21 (typical T.C. 10ppm/°C)

- Low-power design: the typical consumption in normal operation is about 2.6mA.

- Metering Features:

- > 3 independent oversampling  $\Sigma/\Delta$  ADCs: one of the ADC (channel A) can measure voltage, the other ADC with multifunction measure current or temperature etc.

- > Highly Metering Accurate:

- ♦ Supports the requirements of GB/T17215.321-2008/IEC 62053-21:2003, GB/T 17215.322-2008/IEC 62053-22:2003and GB/T 17215.323-2008/IEC 62053-23:2003.

- $\diamond$  Less than 0.1% error in active energy metering over a dynamic range of 5000:1

- ♦ Less than 0.2% error in reactive energy metering over a dynamic range of 5000:1

- ♦ Less than 0.5% error in current/voltage RMS over a dynamic range of 5000:1.

- > Supports various measurements:

- ♦ DC components of voltage and current signal

- ♦ Total /fundamental instantaneous/average current/voltage RMS

- ♦ Total instantaneous/average active /reactive/apparent power

- ♦ 10 or 12 cycles of total RMS

- ♦ Fundamental instantaneous/average active /reactive/apparent power

- Active/reactive energy, active/reactive/apparent power, Irms, constant value, and fundamental wave are selectable

- ♦ Line frequency and phase

- ♦ Temperature

- > DC signals measurement

- Software calibration

- > Accelerating calibration when weak current is applied.

- Supports detection for over-current, over-voltage, under-current, under-voltage, voltage dip, and voltage swell

- Supports waveform buffer and waveform transmitted by DMA

- Supports active upload for energy accumulation

- Current input: current shunt resistor, CT, Rogowski Coil, Hall cell, and TMR supportive

- CTI input clock frequency: 6.5536MHz

- Supports UART communication interface

- Supports SPI communication interface

- Operating Temperature: -40~+85°C

- Storage Temperature: -55~+150°C

- Package: SSOP(M)24, SOP(M)16.

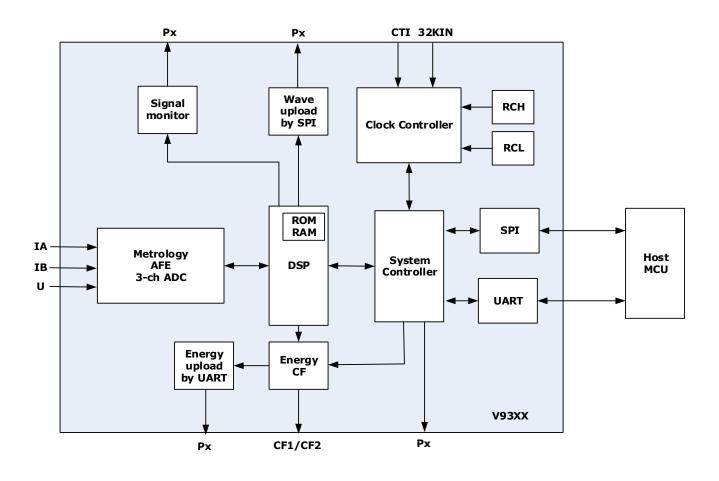

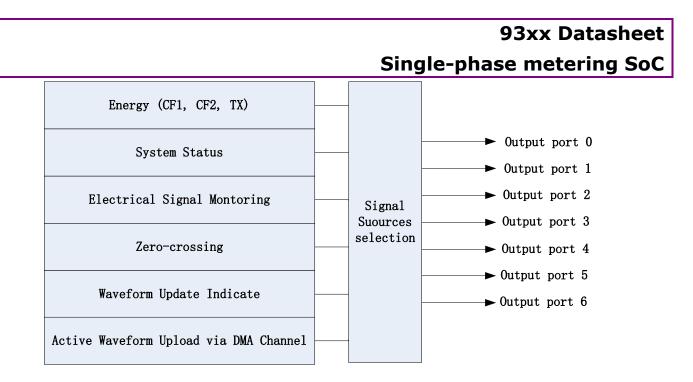

#### 1.1. Functional Block Diagram

Figure 1-1 Functional block diagram

#### 1.2. Pin Description

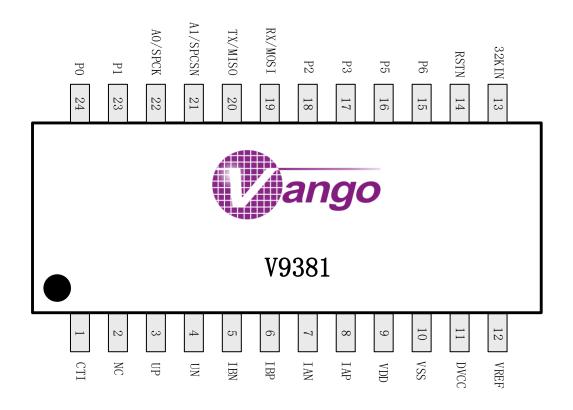

#### 1.2.1. V9381 Pin Description

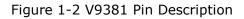

#### 1.2.2. V9360 Pin Description

Figure 1-3 V9360 Pin Description

#### 1.2.3. Pin Description

| Pin No. |       |          |       |                                                                               |

|---------|-------|----------|-------|-------------------------------------------------------------------------------|

| V9381   | V9360 | Mnemonic | Туре  | Description                                                                   |

| 1       | 15    | CTI      | Input | Input pin for 6.5536 MHz clock.                                               |

| 2       | 16    | NC       |       | Floating                                                                      |

| 3       | 1     | UP       | Input | Positive input pin for Voltage Channel Sampling.                              |

| 4       | 2     | UN       | Input | Negative input pin for Voltage Channel Sampling.                              |

| 5       | 3     | IBN      | Input | Negative input pin for current channel B sampling.                            |

| 6       | 4     | IBP      | Input | Positive input pin for current channel B sampling.                            |

| 7       | 5     | IAN      | Input | Negative input pin for current channel A sampling.                            |

| 8       | 6     | IAP      | Input | Positive input pin for current channel A sampling.                            |

| 9       | 9     | VDD      | Power | 3.3V power supply. This pin must be decoupled to a $\ge 0.1 \mu F$ capacitor. |

| 10 | 7  | VSS      | Ground           | Ground                                                                                                                                                                                                                       |

|----|----|----------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11 | 10 | DVCC     | Power            | Digital power output.<br>This pin must be connected to a parallel circuit combined by a $\ge 4.7\mu$ F capacitor and $0.1\mu$ F capacitor, and then grounded.                                                                |

| 12 | 8  | VREF     | Input/<br>Output | On-chip reference voltage.<br>This pin must be connected to a 1µF capacitor, and<br>then grounded.                                                                                                                           |

| 13 | -  | X32KIN   | Input            | 32K CLK input pin (Digital IO interface).                                                                                                                                                                                    |

| 14 | -  | RSTN     | Input            | Reset input, active low.<br>After power on, the "RSTN" could be driven low for<br>at least 2 ms by MCU to force the chip into the reset<br>state.<br>There is a pull-up resistor inside the chip, which is<br>about 50K ohm. |

| 15 | -  | P6       | Output           | CF1/ CF2/ single interruption/ all interruption/<br>automatic data uploads                                                                                                                                                   |

| 16 | -  | Р5       | Output           | CF1/ CF2/ single interruption/ all interruption/<br>automatic data uploads                                                                                                                                                   |

| 17 | 11 | Р3       | Output           | CF1/ CF2/ single interruption/ all interruption/ automatic data uploads                                                                                                                                                      |

| 18 | 12 | P2       | Output           | CF1/ CF2/ single interruption/ all interruption/<br>automatic data uploads                                                                                                                                                   |

| 19 | 13 | RX/MOSI  | Input            | UART communicates with RX pin. / SPI interface in slave mode. It's used for data input.<br>There is a pull-up resistor inside the chip, which is about 50K ohm.                                                              |

| 20 | 14 | TX/MISO  | Output           | UART communicates with TX pin. / SPI interface in slave mode. It's used for data output.<br>There is a pull-up resistor inside the chip, which is about 50K ohm.                                                             |

| 21 | -  | A1/SPCSN | Input            | Address select pin 1 for UART. / Chip select pin for SPI                                                                                                                                                                     |

| 22 | -  | A0/SPCK  | Input            | Address select pin 0 for UART. / SPI interface in slave mode. It's used for clock input.                                                                                                                                     |

| 23 | -  | P1       | Output           | CF1/ CF2/ single interruption/ all interruption/<br>automatic data uploads                                                                                                                                                   |

| 24 | -  | PO       | Output           | CF1/ CF2/ single interruption/ all interruption/ automatic data uploads                                                                                                                                                      |

#### 1.3. Parameters

Table 1-2 Parameters

| Parameter                            | Min. | Тур.   | Max. | Unit       | Description                 |

|--------------------------------------|------|--------|------|------------|-----------------------------|

| ADC                                  |      |        | •    | •          |                             |

| DC Offset                            |      |        | 10   | mV         |                             |

| Resolution                           |      | 23     |      | Bit        | Sign bit is included.       |

| Bandwidth (-3dB)                     | 0.4  | 3.2    | 6.4  | KHz        | Programmable                |

| On-chip Reference                    |      |        |      |            |                             |

| Reference Error                      | -18  |        | 18   | mV         | @ 25°C                      |

| Output Voltage                       |      | 1.21   |      | v          |                             |

| Power Supply Rejection Ratio         |      | 92     |      | dB         |                             |

| Temperature Coefficient              |      | 10     | 30   | ppm/°<br>C |                             |

| Power Input (VDD)                    | 2.6  | 3.3    | 3.6  | V          |                             |

| POR Detection Threshold              | 1.22 | 1.3    | 1.64 | V          | Offset associated with VREF |

| Power-Down Detection Threshold       | 2.6  | 2.8    | 3.1  | V          | Offset associated with VREF |

| Digital Power Output (DVCC)          |      | 1      |      | 1          |                             |

| Voltage                              |      | 1.4    |      | V          |                             |

| Current                              |      |        | 35   | mA         |                             |

| СТІ                                  |      |        |      |            |                             |

| External Input Frequency             |      | 6.5536 |      | MHz        |                             |

| Digital IO, output                   |      |        |      |            |                             |

| Output High Voltage (Vон)            | 2.4  |        |      | V          | Isource=5.6mA               |

| Output Low Voltage (VoL)             |      |        | 0.4  | V          | I <sub>SINK</sub> =5.6mA    |

| Digital IO, input                    |      |        |      |            |                             |

| Input High Voltage (VINH)            | 2.0  |        | 3.6  | V          |                             |

| Input Low Voltage (VINL)             | -0.3 |        | 0.8  | V          |                             |

| Input Current (I <sub>IN</sub> )     |      |        | ±1   | μA         |                             |

| Input Capacitance (C <sub>IN</sub> ) |      |        | 10   | pF         |                             |

| UART Data Rate                       | 1200 |        | 9600 | bps        | Brad rate self-adapting     |

|               |      |        |      | Single | e-phase metering SoC                                                     |

|---------------|------|--------|------|--------|--------------------------------------------------------------------------|

| Parameter     | Min. | Тур.   | Max. | Unit   | Description                                                              |

| SPI Data Rate |      |        | 800  | KHz    | Related to system CLK, the highest speed is one sixteenth of system CLK. |

| RCL frequency | -50% | 32768  | +50% | Hz     |                                                                          |

| RCH frequency | -20% | 6.5536 | +20% | MHz    |                                                                          |

### 1.4. Absolute Maximum Ratings

Operating circumstance exceeding Absolute Maximum Ratings may cause permanent damage to the device.

Table 1-3 Absolute maximum ratings

| Parameter             | Mnemonic        | Min. | Max.  | Unit | Description |

|-----------------------|-----------------|------|-------|------|-------------|

| Analog Power Supply   | VDD             | -0.3 | +3.63 | V    | To ground.  |

| Digital Power Supply  | DVCC            | -0.3 | +1.98 | V    | To ground.  |

| Analog Input Voltage  | IAP/IAN/IBP/IBN | -0.3 | 3.3   | V    | To ground.  |

| Analog Input Voltage  | UP/UN           | -0.3 | 3.3   | V    | To ground.  |

| Operating Temperature |                 | -40  | +85   | °C   |             |

| Storage Temperature   |                 | -55  | +150  | °C   |             |

### 2. Registers

All register will be reset to default value which are hexadecimal when V93XX is in the reset state. There are four kinds of reset conditions, including power on reset (POR) external pin reset, global software reset, and RX reset.

### 2.1. Registers List

Table 2-1 Register list

| Register       | Туре | Address | Description                                              | Default   |

|----------------|------|---------|----------------------------------------------------------|-----------|

| DSP_CTRL0      | R/W  | 0x00    | Analog Control Register 0.                               | 0x0000000 |

| DSP_CTRL1      | R/W  | 0X01    | Analog Control Register 1.                               | 0x0000000 |

| DSP_CTRL0      | R/W  | 0x02    | Metering Control Register 0.                             | 0x0000000 |

| DSP_CTRL1      | R/W  | 0x03    | Metering Control Register 1.                             | 0x0000000 |

| DSP_CTRL2      | R/W  | 0x04    | Metering Control Register 2.                             | 0x0000000 |

| DSP_CTRL3      | R/W  | 0x05    | Metering Control Register 3.                             | 0x0000000 |

| DSP_CTRL4      | R/W  | 0x06    | Metering Control Register 4.                             | 0x0000000 |

| DSP_CTRL5      | R/W  | 0x07    | Metering Control Register 5.                             | 0x0000000 |

| DSP_DAT_PA     | R    | 0x08    | Instantaneous Active Power of channel A.                 |           |

| DSP_DAT_QA     | R    | 0x09    | Instantaneous Reactive Power of channel A.               |           |

| DSP_DAT_SA     | R    | 0x0A    | Instantaneous Apparent Power of channel A.               |           |

| DSP_DAT_PB     | R    | 0x0B    | Instantaneous Active Power of channel B.                 |           |

| DSP_DAT_QB     | R    | 0x0C    | Instantaneous Reactive Power of channel B                |           |

| DSP_DAT_SB     | R    | 0x0D    | Instantaneous Apparent Power of channel B                |           |

| DSP_DAT_RMS0UA | R    | 0x0E    | Instantaneous RMS of Voltage                             |           |

| DSP_DAT_RMS0IA | R    | 0x0F    | Instantaneous RMS of current A.                          |           |

| DSP_DAT_RMS0IB | R    | 0x10    | Instantaneous RMS of Current B.                          |           |

| DSP_DAT_CH1    | R    | 0x11    | Instantaneous Value of Fundamental wave of Channel 1.    |           |

| DSP_DAT_CH2    | R    | 0x12    | Instantaneous Value of Fundamental wave of<br>Channel 2. |           |

| DSP_DAT_PA1    | R    | 0x13    | Average Active Power of Channel A.                       |           |

| DSP_DAT_QA1    | R    | 0x14    | Average Reactive Power of Channel A.                     |           |

| DSP_DAT_SA1    | R    | 0x15    | Average Apparent Power of Channel A                      |           |

| DSP_DAT_PB1    | R    | 0x16    | Average Active power of Channel B                        |           |

| DSP_DAT_QB1    | R    | 0x17    | Average Reactive power of Channel B                      |           |

| DSP_DAT_SB1    | R    | 0x18    | Average Apparent Power of Channel B                      |           |

| DSP_DAT_RMS1U  | R    | 0x19    | Average RMS of Voltage.                                  |           |

| DSP_DAT_RMS1IA | R    | 0x1A    | Average RMS of Current A.                                |           |

|                    |     |      | Single-phase met                                                                                                                                                                             | ering Soc  |

|--------------------|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| DSP_DAT_RMS1IB     | R   | 0x1B | Average RMS of Current B.                                                                                                                                                                    |            |

| DSP_DAT_CH1_AVG    | R   | 0x1C | Average value of Fundamental wave of Channel 1.                                                                                                                                              |            |

| DSP_DAT_CH2_AVG    | R   | 0x1D | Average value of Fundamental wave of Channel 2.                                                                                                                                              |            |

| DSP_DAT_RMSU_AVG   | R   | 0x1E | Average RMS of Voltage for 10 or 12 cycles (chose by line frequency).                                                                                                                        |            |

| DSP_DAT_RMSIA_AVG  | R   | 0x1F | Average RMS of Current IA for 10 or 12 cycles (chose by line frequency).                                                                                                                     |            |

| DSP_DAT_RMSIB_AVG  | R   | 0x20 | Average RMS of Current IB for 10 or 12 cycles (chose by line frequency).                                                                                                                     |            |

| DSP_DAT_FRQ        | R   | 0x21 | Line Frequency.                                                                                                                                                                              |            |

| DSP_DAT_DCU        | R   | 0x22 | DC value of voltage channel.                                                                                                                                                                 |            |

| DSP_DAT_DCIA       | R   | 0x23 | DC value of current channel A.                                                                                                                                                               |            |

| DSP_DAT_DCIB       | R   | 0x24 | DC value of Current channel B.                                                                                                                                                               |            |

| DSP_CFG_CALI_PA    | R/W | 0x25 | To set gain calibration for the active power A.                                                                                                                                              | 0x00000000 |

| DSP_CFG_DC_PA      | R/W | 0x26 | To set offset calibration for the active power A.                                                                                                                                            | 0x00000000 |

| DSP_CFG_CALI_QA    | R/W | 0x27 | To set gain calibration for Reactive power A.                                                                                                                                                | 0x00000000 |

| DSP_CFG_DC_QA      | R/W | 0x28 | To set offset calibration for Reactive power A.                                                                                                                                              | 0x00000000 |

| DSP_CFG_CALI_PB    | R/W | 0x29 | To set gain calibration for Active power B.                                                                                                                                                  | 0x00000000 |

| DSP_CFG_DC_PB      | R/W | 0x2A | To set offset calibration for Active power B.                                                                                                                                                | 0x00000000 |

| DSP_CFG_CALI_QB    | R/W | 0x2B | To set gain calibration for Reactive power B.                                                                                                                                                | 0x00000000 |

| DSP_CFG_DC_QB      | R/W | 0x2C | To set offset calibration for Reactive power B.                                                                                                                                              | 0x00000000 |

| DSP_CFG_CALI_RMSU  | R/W | 0x2D | To set gain calibration for Voltage RMS.                                                                                                                                                     | 0x00000000 |

| DSP_CFG_RMS_DCU    | R/W | 0x2E | To set offset calibration for Voltage RMS.                                                                                                                                                   | 0x00000000 |

| DSP_CFG_CALI_RMSIA | R/W | 0x2F | To set gain calibration for Current RMS A.                                                                                                                                                   | 0x00000000 |

| DSP_CFG_RMS_DCIA   | R/W | 0x30 | To set offset calibration for Current RMS A.                                                                                                                                                 | 0x0000000  |

| DSP_CFG_CALI_RMSIB | R/W | 0x31 | To set gain calibration for Current RMS B.                                                                                                                                                   | 0x0000000  |

| DSP_CFG_RMS_DCIB   | R/W | 0x32 | To set offset calibration for Current RMS B.                                                                                                                                                 | 0x0000000  |

| DSP_CFG_PHC        | R/W | 0x33 | Phase Error Calibration Register.<br>[10:0]= phase error calibration value for<br>channel A<br>[26:16]= phase error calibration value for<br>channel B, where the range is from<br>-766~767. | 0x00000000 |

| DSP_CFG_DCU        | R/W | 0x34 | To set the DC calibration for the voltage channel.                                                                                                                                           | 0x00000000 |

| DSP_CFG_DCIA       | R/W | 0x35 | To set the DC calibration for the current channel A.                                                                                                                                         | 0x00000000 |

| DSP_CFG_DCIB       | R/W | 0x36 | To set the DC calibration for the current channel B.                                                                                                                                         | 0x00000000 |

|               | 93xx Datasheet            |      |                                                                                                                                                                                                                                                                                                                                                  |            |  |  |  |  |

|---------------|---------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--|--|--|--|

|               | Single-phase metering SoC |      |                                                                                                                                                                                                                                                                                                                                                  |            |  |  |  |  |

| DSP_CFG_BPF   | R/W                       | 0x37 | Band-pass filter coefficient. Related to setting<br>the DSP_MODE by Bit[7:4] of metering control<br>register 0 (0x02,DSP_CTRL0).<br>Setting 0x806764B6 at DSP_MODE=0, 1, 2;<br>Setting 0x80DD7A8C at DSP_MODE=6,7;<br>Setting 0x82B465F0 at DSP_MODE=8.<br>The frequency of other modes would be not<br>supported to measure, so setting to 0x0. | 0x00000000 |  |  |  |  |

| DSP_CFG_CKSUM | R/W                       | 0x38 | Configuration register for checksum.                                                                                                                                                                                                                                                                                                             | 0x0000000  |  |  |  |  |

| EGY_PROCTH    | R/W                       | 0x39 | Anti-creep threshold for energy accumulator.<br>When the accumulated value of the anti-creep<br>energy accumulator over this threshold and the<br>accumulated value of the high-speed energy<br>accumulator under this threshold, the<br>accumulated value of the high-speed energy<br>accumulator will be cleared.                              | 0×00000000 |  |  |  |  |

| EGY_PWRTH     | R/W                       | 0x3A | Accumulation threshold for energy accumulator.<br>Because the energy accumulator was 46Bit, the<br>accumulated value of the high-speed energy<br>accumulator equals to this threshold*16384;<br>the accumulated value of the low-speed energy<br>accumulator equals to this value*4.                                                             | 0×00000000 |  |  |  |  |

| EGY_CONST1    | R/W                       | 0x3B | Energy accumulator 1 accumulating constant.                                                                                                                                                                                                                                                                                                      | 0x0000000  |  |  |  |  |

| EGY_OUT1L     | R/W                       | 0x3C | Energy accumulator 1 accumulating lower bit.                                                                                                                                                                                                                                                                                                     | 0x0000000  |  |  |  |  |

| EGY_OUT1H     | R/W                       | 0x3D | Energy accumulator 1 accumulating higher bit.<br>Effective for lower 14 bit.                                                                                                                                                                                                                                                                     | 0×00000000 |  |  |  |  |

| EGY_CFCNT1    | R                         | 0x3E | Energy accumulator 1 pulse counter.                                                                                                                                                                                                                                                                                                              | 0x0000000  |  |  |  |  |

| EGY_CONST2    | R/W                       | 0x3F | Energy accumulator 2 accumulating constant.                                                                                                                                                                                                                                                                                                      | 0x0000000  |  |  |  |  |

| EGY_OUT2L     | R/W                       | 0x40 | Energy accumulator 2 accumulating lower bit.                                                                                                                                                                                                                                                                                                     | 0x0000000  |  |  |  |  |

| EGY_OUT2H     | R/W                       | 0x41 | Energy accumulator 2 accumulating higher bit.<br>Effective for lower 14 bit.                                                                                                                                                                                                                                                                     | 0×00000000 |  |  |  |  |

| EGY_CFCNT2    | R                         | 0x42 | Energy accumulator 2 pulse counter.                                                                                                                                                                                                                                                                                                              | 0x0000000  |  |  |  |  |

| EGY_CONST3    | R/W                       | 0x43 | Energy accumulator 3 accumulating constant.                                                                                                                                                                                                                                                                                                      | 0x00000000 |  |  |  |  |

| EGY_OUT3      | R/W                       | 0x44 | Energy accumulator 3 accumulating value.                                                                                                                                                                                                                                                                                                         | 0x0000000  |  |  |  |  |

| EGY_CFCNT3    | R                         | 0x45 | Energy accumulator 3 pulse counter.                                                                                                                                                                                                                                                                                                              | 0x0000000  |  |  |  |  |

| EGY_CONST4    | R/W                       | 0x46 | Energy accumulator 4 accumulating constant.                                                                                                                                                                                                                                                                                                      | 0x0000000  |  |  |  |  |

| EGY_OUT4      | R/W                       | 0x47 | Energy accumulator 4 accumulating value.                                                                                                                                                                                                                                                                                                         | 0x0000000  |  |  |  |  |

| EGY_CFCNT4    | R                         | 0x48 | Energy accumulator 4 pulse counter.                                                                                                                                                                                                                                                                                                              | 0x0000000  |  |  |  |  |

| EGY_CONST5    | R/W                       | 0x49 | Energy accumulator 5 accumulating constant.                                                                                                                                                                                                                                                                                                      | 0x0000000  |  |  |  |  |

| EGY_OUT5      | R/W                       | 0x4A | Energy accumulator 5 accumulating value.                                                                                                                                                                                                                                                                                                         | 0x0000000  |  |  |  |  |

| EGY_CFCNT5    | R                         | 0x4B | Energy accumulator 5 pulse counter.                                                                                                                                                                                                                                                                                                              | 0x0000000  |  |  |  |  |

| EGY_CONST6    | R/W                       | 0x4C | Energy accumulator 6 accumulating constant.                                                                                                                                                                                                                                                                                                      | 0x0000000  |  |  |  |  |

|               |     |      | Single-phase met                                                                            | lering Soc |

|---------------|-----|------|---------------------------------------------------------------------------------------------|------------|

| EGY_OUT6      | R/W | 0x4D | Energy accumulator 6 accumulating value.                                                    | 0x00000000 |

| EGY_CFCNT6    | R   | 0x4E | Energy accumulator 6 pulse counter.                                                         | 0x00000000 |

| EGY_CONST7    | R/W | 0x4F | Energy accumulator 7 accumulating constant.                                                 | 0x0000000  |

| EGY_OUT7      | R/W | 0x50 | Energy accumulator 7 accumulating value.                                                    | 0x0000000  |

| EGY_CFCNT7    | R   | 0x51 | Energy accumulator 7 pulse counter.                                                         | 0x00000000 |

| EGY_CONST8    | R/W | 0x52 | Energy accumulator 8 accumulating constant.                                                 | 0x0000000  |

| EGY_OUT8      | R/W | 0x53 | Energy accumulator 8 accumulating value.                                                    | 0x00000000 |

| EGY_CFCNT8    | R   | 0x54 | Energy accumulator 8 pulse counter.                                                         | 0x00000000 |

| DSP_OV_THL    | R/W | 0x55 | To set the lower threshold for the power-creep detection.                                   | 0x0000000  |

| DSP_OV_THH    | R/W | 0x56 | To set the upper threshold for the power-creep detection.                                   | 0x0000000  |

| DSP_SWELL_THL | R/W | 0x57 | To set the lower threshold for the voltage swell.                                           | 0x00000000 |

| DSP_SWELL_THH | R/W | 0x58 | To set the upper threshold for the voltage dip.                                             | 0x00000000 |

| DSP_DIP_THL   | R/W | 0x59 | To set the lower threshold for the voltage dip.                                             | 0x0000000  |

| DSP_DIP_THH   | R/W | 0x5A | To set the upper threshold for the voltage dip.                                             | 0x0000000  |

| FD_OVTH       | R/W | 0x5B | To set over-voltage threshold for fast detection.<br>Bit width is 30bit.                    | 0x00000000 |

| FD_LVTH       | R/W | 0x5C | To set under-voltage threshold for fast detection. Bit width is 30bit.                      | 0×00000000 |

| FD_IA_OCTH    | R/W | 0x5D | To set over-current threshold in current channel A for fast detection. Bit width is 30bit.  | 0×00000000 |

| FD_IA_LCTH    | R/W | 0x5E | To set under-current threshold in current channel A for fast detection. Bit width is 30bit. | 0×00000000 |

| FD_IB_OCTH    | R/W | 0x5F | To set over-current threshold in current channel B for fast detection. Bit width is 30bit.  | 0×00000000 |

| FD_IB_LCTH    | R/W | 0x60 | To set under-current threshold in current channel B for fast detection. Bit width is 30bit. | 0×00000000 |

| DSP_PHS_STT   | R/W | 0x61 | To control the phase measurement. Enable phase measurement once for writing operation.      |            |

| DSP_PHS_U     | R   | 0x62 | Voltage phase.                                                                              | 1          |

| DSP_PHS_UN    | R   | 0x63 | Voltage waveform data which before zero-<br>crossing.                                       | 0          |

| DSP_PHS_UP    | R   | 0x64 | Voltage waveform data which after zero-<br>crossing.                                        | 0×80000000 |

| DSP_PHS_I     | R   | 0x65 | Current phase. 1                                                                            |            |

| DSP_PHS_IN    | R   | 0x66 | Current waveform data which before zero-<br>crossing.                                       | 0          |

| DSP_PHS_IP    | R   | 0x67 | Current waveform data which after zero-<br>crossing.                                        | 0x80000000 |

Single-phase metering SoC

| Single-phase metering Soc |     |      |                                                                                                                                                                                                                 |            |  |

|---------------------------|-----|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--|

| TEMPERATE                 | R   | 0x68 | Temperature Register.                                                                                                                                                                                           | 0          |  |

| DAT_WAVE                  | R   | 0x69 | Waveform data reading. It can repeatable<br>reading the address and obtain the overall<br>waveform data. If there is no need to read all<br>data, it would be reset the bit 31 of DSP_CTRL5<br>to read address. | 0          |  |

| DAT_SWELL_CNT             | R/C | 0x6A | Voltage swell time records, half-wave as unit.<br>Effective as 24bit. Writing any value into this<br>address would be clear this counter to zero.                                                               | 0          |  |

| DAT_DIP_CNT               | R/C | 0x6B | Voltage dip time records, half wave as unit.<br>Effective as 24bit. Writing any value into this<br>address would be clear this counter to zero.                                                                 | 0          |  |

| SYS_SFTRST                | w   | 0x6C | Software reset register.<br>Writing 0x4572beaf into this address would be<br>happen software reset once.                                                                                                        |            |  |

| SYS_BAUDCNT1              | R   | 0x70 | This register stores the system clock count value of the first bit of the UART frame header sent by V93XX.                                                                                                      |            |  |

| SYS_BAUDCNT8              | R   | 0x71 | This register stores the system clock count value of the 8 bits of the UART frame header received by V93XX.                                                                                                     |            |  |

| SYS_INTSTS                | R/C | 0x72 | Interrupt status register.                                                                                                                                                                                      |            |  |

| SYS_INTEN                 | R/W | 0x73 | Interrupt enable register.                                                                                                                                                                                      | 0x00000000 |  |

| SYS_STS                   | R   | 0x74 | System status register.                                                                                                                                                                                         |            |  |

| SYS_MISC                  | R/W | 0x75 | System control register.                                                                                                                                                                                        |            |  |

| SYS_BLK0_ADDR             | R/W | 0x79 | Register for block reading address 0.                                                                                                                                                                           | 0          |  |

| SYS_BLK1_ADDR             | R/W | 0x7A | Register for block reading address 1.                                                                                                                                                                           | 0          |  |

| SYS_BLK2_ADDR             | R/W | 0x7B | Register for block reading address 2.                                                                                                                                                                           | 0          |  |

| SYS_BLK3_ADDR             | R/W | 0x7C | Register for block reading address 3.                                                                                                                                                                           | 0          |  |

| SYS_IOCFGX0               | R/W | 0x7D | Output configuration register for P0, P1, P2 and P3.                                                                                                                                                            | 0          |  |

| SYS_IOCFGX1               | R/W | 0x7E | Output configuration register for P4, P5 and P6.                                                                                                                                                                | 0          |  |

| SYS_VERSION               | R   | 0x7F | Present hardware version.                                                                                                                                                                                       |            |  |

|                           |     |      |                                                                                                                                                                                                                 |            |  |

### 2.2. Analog Control Registers

When power-on reset (POR), RSTN pin reset, RX reset, or global software reset occurs, all analog control registers will be reset to the default value. The default value in the following tables of this section are in format of hexadecimal.

The address range of Analog Control Register is  $0x00 \sim 0x01$  which all is readable and writable. Also, all the metering control registers need to be configuration verification and self-checking.

#### 2.2.1. ANA\_CTRL0 Register

| 0x00, R/W | l, Analog Control | Register 0, ANA_ | CTRL0                                                                                                                                               |

|-----------|-------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit       |                   | Default Value    | Description                                                                                                                                         |

| 31:19     | Reserved          | 0                | These bits must hold its default value for proper operation.                                                                                        |

| 18        | RCHX1P2           | 0                | To enable the increase 6.5M RC oscillator frequency by<br>1.2X. It needs to set to 1 when the line frequency equals<br>to 60Hz.<br>0: X1<br>1: X1.2 |

| 17:14     | Reserved          | 0                | These bits must hold its default value for proper operation.                                                                                        |

| 13        | MEA               | 0                | To select the analog input for Channel IB.<br>0: differential IB input<br>1: internal temperature sensor                                            |

| 12        | Reserved          | 0                | The bit must hold its default value for proper operation.                                                                                           |

| 11        | SHORT_I           | 0                | Current IA and current IB channel ADC input short<br>circuit.<br>0: short circuit<br>1: Normal                                                      |

| 10        | SHORT_V           | 0                | Voltage U channel ADC input short circuit.<br>0: short circuit<br>1: Normal                                                                         |

| 9:0       | Reserved          | 0                | These bits must hold its default value for proper operation.                                                                                        |

Table 2-2 Analog Control Register 0 (0x00, ANA\_CTRL0)

#### 2.2.2. ANA\_CTRL1 Register

Table 2-3 Analog Control Register 1 (0x01, ANA\_CTRL1)

| Default                           |              |       |                                                                                     |  |

|-----------------------------------|--------------|-------|-------------------------------------------------------------------------------------|--|

| Bit                               |              | Value | Description                                                                         |  |

|                                   |              |       | The options of clock frequency divider rate for the ADC 00 corresponds to 819.2KHz. |  |

|                                   |              |       | 00: ×1                                                                              |  |

| 31:30                             | ADCKSEL[1:0] | 0     | 01: ×2                                                                              |  |

|                                   |              |       | 10: ×1/4                                                                            |  |

|                                   |              |       | 11: ×1/2                                                                            |  |

| 29:24                             | RCHTRIM[5:0] | 0     | To adjust the 6.5M RC frequency.<br>000000~011111: step-up the frequency by 1.25%   |  |

|                                   |              |       | 100000~111111: step-down the frequency by 1.25%                                     |  |

| 23                                | Reserved     | 0     | The bit must hold its default value for proper operation.                           |  |

|                                   |              |       | To enable the 6.5M RC oscillator.                                                   |  |

| 22                                |              |       | 0: enable                                                                           |  |

| 22                                | RCCLK_PD     | 0     | 1: disable                                                                          |  |

|                                   |              |       | This bit must be set to 0 for proper operation.                                     |  |

| 21:15                             | Reserved     | 0     | These bits must hold its default value for proper operation.                        |  |

|                                   |              |       | To adjust the gain of current ADC in the channel B.                                 |  |

|                                   |              |       | 000: 4                                                                              |  |

|                                   |              |       | 001: 1                                                                              |  |

| 14:12                             | GIB[2:0]     | 0     | 010: 32                                                                             |  |

|                                   |              |       | 011: 16                                                                             |  |

|                                   |              |       | 100/101/110/111: prohibited                                                         |  |

|                                   |              |       | GIB[2:0] is recommended set to 000 for proper operation.                            |  |

|                                   |              |       | To adjust the gain of voltage ADC.                                                  |  |

| 11                                | GU           | 0     | 0:8                                                                                 |  |

|                                   | 0            | 1:4   |                                                                                     |  |

|                                   |              |       | This bit must be set to 0 for proper operation.                                     |  |

|                                   |              |       | To adjust the gain of current ADC in the channel A.                                 |  |

| 10:8                              | GIA[2:0]     | 0     | 000: 32                                                                             |  |

|                                   |              |       | 001: 16                                                                             |  |

| Vango Technologies, Inc. 23 / 117 |              |       |                                                                                     |  |

Single-phase metering SoC

| 0x01, R/W, Analog Control Register 1, ANA_CTRL1 |            |                  |                                                                                                                                                                                                     |  |

|-------------------------------------------------|------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Bit                                             |            | Default<br>Value | Description                                                                                                                                                                                         |  |

|                                                 |            |                  | 010: 4<br>011: 1<br>100~111: prohibited<br>GIA[2: 0] is recommended set to 000 for proper operation.                                                                                                |  |

| 7                                               | XRST_PD    | 0                | The external input CTI clock enable.<br>0: enable<br>1: disable                                                                                                                                     |  |

| 6:5                                             | Reserved   | 0                | These bits must hold its default value for proper operation.                                                                                                                                        |  |

| 4:3                                             | RESTL[1:0] | 0                | To roughly adjust the temperature coefficient of the<br>Bandgap circuit.<br>00: 0 ppm<br>01: -58 ppm<br>10: +111 ppm<br>11: +56 ppm                                                                 |  |

| 2:0                                             | REST[2:0]  | 0                | To finely adjust the temperature coefficient of the Bandgap<br>circuit.<br>000: 0 ppm<br>001: +7 ppm<br>010: +14 ppm<br>011: +28 ppm<br>100: -32 ppm<br>101: -21 ppm<br>110: -14 ppm<br>111: -7 ppm |  |

#### 2.3. System Control & Status Register

When power-on reset (POR), RSTN pin reset, RX reset, or global software reset occurs, all system control registers will be reset to the default value. The default value in the following tables of this section are in format of hexadecimal.

In the V93XX, the mainly functions of System Control Register is controlling interface, interrupt, RAM, and IO output. SYS\_INTEN (0x73) controls enable interruption, SYS\_INTSYS (0x72) is interrupted status register. Bit[4: 0] of SYS\_MISC (0x75) are used for configuring the interface operation, interrupting pin output whether reverse, whether turn off the energy accumulator when power down and whether turn

#### Single-phase metering SoC

off the energy accumulator when in wrong calibration. SYS\_RAMADDR (0x77) is controlling internal RAM address. SYS\_RAMDATA is internal RAM data registers. SYS\_BLK0\_ADDR~SYS\_BLK3\_ADDR are blocked reading address. SYS\_IOCFGX0~SYS\_IOCFGX1 are the control register of IO output

#### 2.3.1. SYS\_BAUDCNT1 Register

Table 2-4 UART transmitting data 1bit count value (0x70, SYS\_BAUDCNT1)

| 0x70, L | 0x70, UART transmitting data 1bit count value, SYS_BAUDCNT1 |                   |   |                                                                                                            |  |  |  |  |

|---------|-------------------------------------------------------------|-------------------|---|------------------------------------------------------------------------------------------------------------|--|--|--|--|

| bit     |                                                             | R/W Default Value |   | Description                                                                                                |  |  |  |  |

| 31:14   | -                                                           | -                 | - | Reserved.                                                                                                  |  |  |  |  |

| 13:0    | BAUDCNT1                                                    | R                 |   | This register stores the system clock count value of the first bit of the UART frame header sent by V93XX. |  |  |  |  |

#### 2.3.2. SYS\_BAUDCNT8 Register

| Table 2-5 UART | receiving da | ata 8bit count | value (0x71 | , SYS_ | _BAUDCNT8) |

|----------------|--------------|----------------|-------------|--------|------------|

|----------------|--------------|----------------|-------------|--------|------------|